聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

Xilinx

+關(guān)注

關(guān)注

73文章

2190瀏覽量

129436 -

Vivado

+關(guān)注

關(guān)注

19文章

844瀏覽量

70347

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

vivado時(shí)序分析相關(guān)經(jīng)驗(yàn)

vivado綜合后時(shí)序?yàn)槔饕怯袃煞N原因?qū)е拢?1,太多的邏輯級(jí)

2,太高的扇出

分析時(shí)序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

發(fā)表于 10-30 06:58

vcs和vivado聯(lián)合仿真

我們?cè)谧鰠①愓n題的過(guò)程中發(fā)現(xiàn),上FPGA開發(fā)板跑系統(tǒng)時(shí),有時(shí)需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對(duì)添加了vivado ip核的soc系統(tǒng)進(jìn)行仿真。在這種情況下

發(fā)表于 10-24 07:28

Vivado中向FPGA的Flash燒錄e203的方法

首先導(dǎo)入、并配置好項(xiàng)目,完成項(xiàng)目的綜合(SYNTHESIS)與實(shí)現(xiàn)(IMPLEMENTATION),查看有無(wú)錯(cuò)誤與或警告信息,調(diào)整完成后,右鍵比特流生成(Generate Bitstream),選擇

發(fā)表于 10-23 08:28

vivado仿真時(shí)GSR信號(hào)的影響

利用vivado進(jìn)行設(shè)計(jì)xilinx FPGA時(shí),寫完設(shè)計(jì)代碼和仿真代碼后,點(diǎn)擊run simulation(啟動(dòng)modelsim進(jìn)行仿真)。

Vivado無(wú)法選中開發(fā)板的常見原因及解決方法

在使用 AMD Vivado Design Suite 對(duì)開發(fā)板(Evaluation Board)進(jìn)行 FPGA 開發(fā)時(shí),我們通常希望在創(chuàng)建工程時(shí)直接選擇開發(fā)板,這樣 Vivado 能夠自動(dòng)配置

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結(jié)果(以 Vivado 2024.2 為例)。

Vivado 2018.3軟件的使用教程

大家好,歡迎來(lái)到至芯科技FPGA煉獄營(yíng)地,準(zhǔn)備開啟我們的偉大征程!正所謂“兵馬未動(dòng),糧草先行”,戰(zhàn)前的準(zhǔn)備自是必不可少,在FPGA的漫漫沙場(chǎng),我們何以入場(chǎng),何以取勝呢?在這里我們?yōu)楦魑粦?zhàn)友準(zhǔn)備了vivado 2018.3的使用教程。

AMD Vivado Design Suite IDE中的設(shè)計(jì)分析簡(jiǎn)介

本文檔涵蓋了如何驅(qū)動(dòng) AMD Vivado Design Suite 來(lái)分析和改善您的設(shè)計(jì)。

Vivado Design Suite用戶指南: 設(shè)計(jì)分析與收斂技巧

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南: 設(shè)計(jì)分析與收斂技巧.pdf》資料免費(fèi)下載

發(fā)表于 01-15 15:28

?2次下載

Vivado Design Suite用戶指南:邏輯仿真

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:邏輯仿真.pdf》資料免費(fèi)下載

發(fā)表于 01-15 15:25

?0次下載

使用HLS流程設(shè)計(jì)和驗(yàn)證圖像信號(hào)處理設(shè)備

STMicroelectronics成像部門負(fù)責(zé)向消費(fèi)者、工業(yè)、安全和汽車市場(chǎng)提供創(chuàng)新的成像技術(shù)和產(chǎn)品。該團(tuán)隊(duì)精心制定了一套通過(guò)模板實(shí)現(xiàn)的High-Level Synthesis(HLS)高層次綜合流程,使得上述產(chǎn)品能夠迅速上市。對(duì)于汽車市場(chǎng),該流程符合ISO 26262

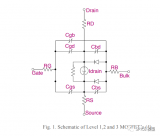

從Level1 Model到Level3 Modle來(lái)感受器件模型是如何開發(fā)的

? ? ? ?本文從Level1 model到Level3 model的Ids電流公式的發(fā)展來(lái)感受Compact器件模型是如何開發(fā)的。 MOS技術(shù)擴(kuò)展到納米尺寸,帶來(lái)了電路模擬器中器件模型的發(fā)展

求助,ISO7721用于485隔離遇到的疑問(wèn)求解

我想選用ISO7721用于485隔離,遇到帶你問(wèn)題,請(qǐng)幫忙看看。

①看到PDF上描述IIH(High-level input current)最大到10uA,但是MCU SCI TX引腳輸出一般

發(fā)表于 12-18 06:30

Xilinx_Vivado_SDK的安裝教程

I Agree,然后點(diǎn)擊 Next: 選擇 Vivado HL System Edition(一般選擇這個(gè)設(shè)計(jì)套件比較完整,它比 Vivado HL Design Edition 多了一個(gè) System Generator for DSP with Mat

每次Vivado編譯的結(jié)果都一樣嗎

很多FPGA工程師都有這種困惑,Vivado每次編譯的結(jié)果都一樣嗎? 在AMD官網(wǎng)上,有這樣一個(gè)帖子: Are Vivado results repeatable for identical

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

評(píng)論